# Wireless 2.4GHz 500mW Transceiver RF Module

## **Version History**

| Version | Date          | Changes                  |

|---------|---------------|--------------------------|

| V1.0    | Feb. 22, 2012 | 1 <sup>st.</sup> Edition |

WENSHING **TRW-24HP-N** wireless 2.4GHz hi power transceiver RF module is designed, developed and manufactured as contemplated for general use, without limitation, ordinary industrial use, general office use, personal use, and household use, but is not designed, developed and manufactured as contemplated:

- (1) For use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system).

- (2) For use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

You shall not use this product for the above-mentioned using.

If your equipment is likely to be used for the above-mentioned uses, please consult with our sales representative before using.

WENSHING Component Division shall not be liable against you and/or any third party for any claims or damages arising

in connection with the above-mentioned uses of this product.

#### **Function Introduction**

- TRW-24HP-N wireless 2.4GHz High power transceiver RF module is a frequency agile, half duplex.

- Transceiver is with SPI bus interface.

- Direct microprocessor

- Connection for control and data transfer eliminates.

- Needs for additional ICs, while integrated data code/decode hardware.

- Reduces the instruction set requirements on the associated microprocessor.

- Adjustable data rates, filter bandwidths and detection.

- Levels allow the IC to be used in a wide variety of high sensitivity/ High EMI environments. The TRW-24HP-N is ideally suitable for use in battery powered wireless applications in conjunction with Microprocessors for data communication.

### **Application**

- Security System

- 2.4 GHz Cordless Phones

- Wireless Remote Control Car

- Wireless Remote Control Robot

- Automatic Power Switch Control

- Wireless Modem

## **Specification**

- Frequency Range: 2.400GHz~2.4835GHz

- GFSK modulation

- Output Power: 23±1dbm (5V)

- Data Rates: from 1 to 2M bits/Sec

- Low Working Voltage: 3.7V~5.5V

- Input sensitivity: -95 dBm

- 3 separate 32 bytes TX and RX FIFOs

- Automatic packet handling

- RF Channels: 126

- Built-in antenna connector

- RoHS Compliant

| Parameter               | Sp<br>Min | ecificat<br>Type | ion<br>Max | Unit  | Condition              |

|-------------------------|-----------|------------------|------------|-------|------------------------|

| Frequency Range         | 2.4       |                  | 2.4835     | GHz   |                        |

| Receiver Sensitivity    | -98       |                  | -91        | dBm   | 1Mbps                  |

| Data Rate               | 1         |                  | 2          | M Bit | GFSK                   |

| Supply Voltage, VDD     | 3.7       |                  | 5.5        | V     | DC                     |

| TX Current              |           |                  |            | mA    |                        |

| RX Current              |           |                  |            | mA    |                        |

| Power down Current      |           | 1                |            | uA    | Power down Mode        |

| standby-I mode Current  |           | 26               |            | uA    | standby-I mode         |

| standby-II mode Current |           | 360              |            | uA    | standby-II mode        |

| Disable Current         |           |                  |            | uA    | Enable PIN is LO       |

| Power up time           |           |                  | 100        | ms    | Disable to Enable time |

| Operating Temperature   | -20       |                  | +70        | °C    |                        |

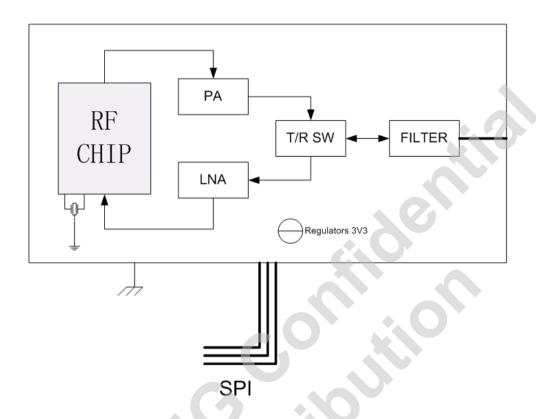

# **Internal Block Diagram**

# **Absolute maximum ratings**

| Minimum         | Maximum    | Units | Operating conditions |

|-----------------|------------|-------|----------------------|

| Supply voltages |            |       |                      |

| -0.3            | 5.5        | V     | VDD                  |

|                 | 0          | V     | GND                  |

| Input voltage   |            |       |                      |

| -0.3            | 3.6        | V     | VI(DATA IN)          |

| Output voltage  |            | •     |                      |

| GND TO 3        | GND TO 3.3 | V     | VO                   |

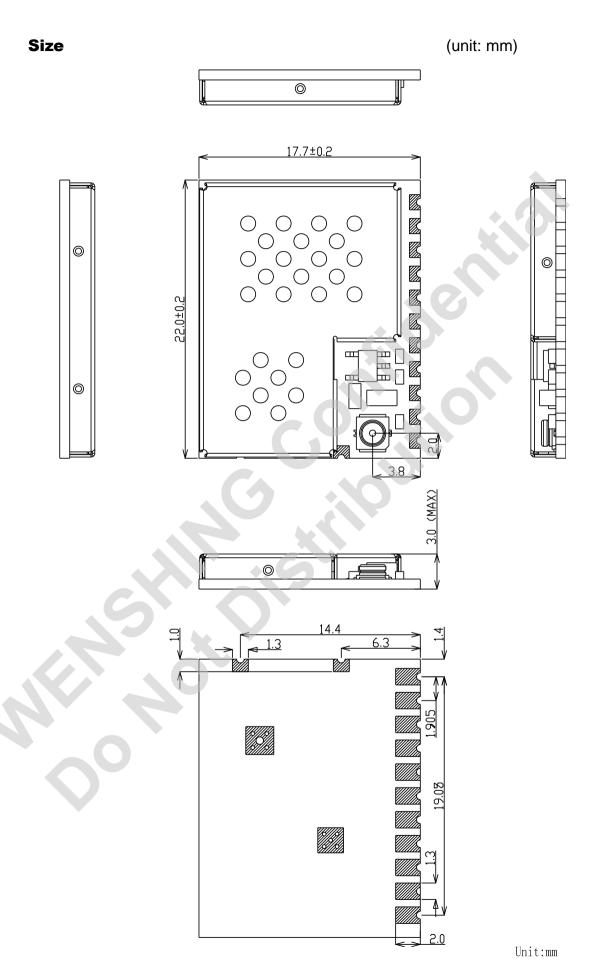

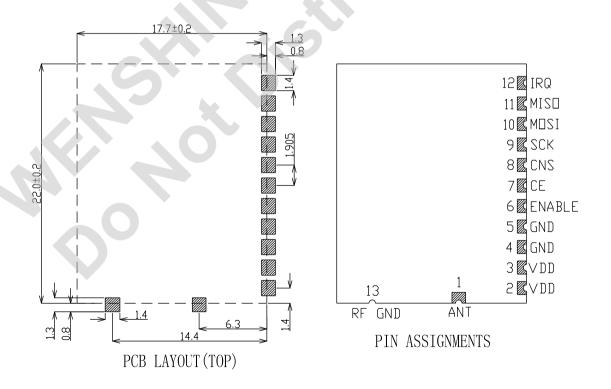

# **Pin Assignment**

| Pin | Name    | I/O    | Description                                              |

|-----|---------|--------|----------------------------------------------------------|

| 1   | Antenna | I/O    | RF output to the antenna                                 |

| 2   | VDD     | POWER  | Power Supply 3.7~5.5V                                    |

| 3   | VDD     | POWER  | Power Supply 3.7~5.5V                                    |

| 4   | GND     | Ground | Ground                                                   |

| 5   | GND     | Ground | Ground                                                   |

| 6   | ENABLE  | I      | Full power down 0 = full power down mode 1 = normal mode |

| 7   | CE      | I      | Chip Enable Activates RX or TX mode                      |

| 8   | CNS     | I      | SPI Chip Select                                          |

| 9   | SCK     | I      | SPI Clock                                                |

| 10  | MOSI    | I      | SPI Slave Data Input                                     |

| 11  | MISO    | 0      | SPI Slave Data Output                                    |

| 12  | IRQ     | 0      | Mask able interrupt pin. Active low                      |

| 13  | RF GND  |        | RF Ground                                                |

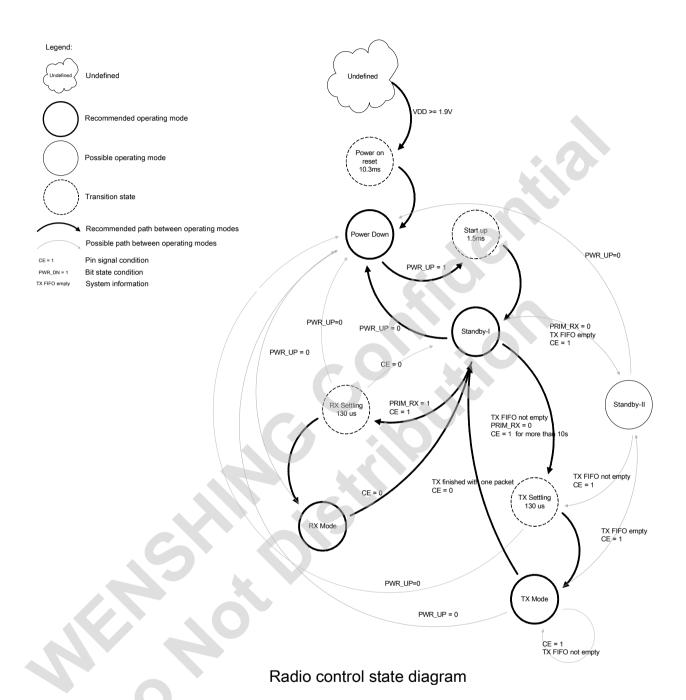

### 電源管理

TRW-24HP-N 模組本身含有穩壓 IC,外部輸入電源可由 3.7~5.5V 輸入,由硬體控制模組本 ENABLE PIN 為 LO 時,模組不會耗電;如由 SPI 介面宣告,也可直接宣告幾個省電模式:

#### Power down Mode

透過 SPI 介面通訊,設定模組內 PWR\_UP 暫存器 BIT 設為 0

#### ● Standby -I Mode

當 PWR\_UP 暫存器 BIT 設為 1 後就為待機模式,此時模組的 Crystal 起振,等待下個指令要求,如此可縮短 RF 要運作時啟動時間。

#### ● Standby -II Mode

當 PWR\_UP 暫存器 BIT 設為 1 後,模組 CE PIN 設為高電位,此時 FIFO 資料開始傳輸,模組 PLL 便開始啟動。

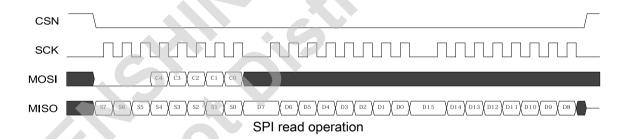

#### SPI 通訊

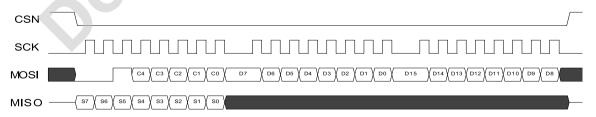

當 MCU對 RF Module 讀 REGISTER時,下圖是時序圖,讀時有前幾位元都是 LO,因 REGISTE 位置沒超過 32,寫入方式是:MCU 對 RF Module 要寫入時,第 5 位元一定要為 1 才允寫入。

#### SPI 讀取時序圖

#### SPI 寫入時序圖

SPI write operation

# 暫存器介紹說明

註:暫存器位置 18H 至 1BH 是模組測試用,請勿使用。

| Г | 叮.          | 首付品位直 1011主                                   | / _ [. | ンイルオブハンジロア(/ | 17 1月 77 19 | \ / I3<br>                                                                                                                            |  |  |  |  |  |

|---|-------------|-----------------------------------------------|--------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   | 位置<br>(Hex) | 旗標名                                           | 位元     | 復位<br>狀態     | 讀寫<br>類型    | 說明1(暫存器8位元)                                                                                                                           |  |  |  |  |  |

|   |             | 設定模組通訊對應 MCU 所需要的功能                           |        |              |             |                                                                                                                                       |  |  |  |  |  |

|   |             | Reserved                                      | 7      | 0            | R/W         | Only '0' allowed.                                                                                                                     |  |  |  |  |  |

|   |             | MASK_RX_DR                                    | 6      | 0            | R/W         | Mask interrupt caused by RX_DR  1: Interrupt not reflected on the IRQ pin  0: Reflect RX_DR as active low interrupt on the IRQ pin.   |  |  |  |  |  |

|   |             | MASK_TX_DS                                    | 5      | 0            | R/W         | Mask interrupt caused by TX_DS  1: Interrupt not reflected on the IRQ pin  0: Reflect TX_DS as active low interrupt on the IRQ pin.   |  |  |  |  |  |

|   | 00          | MASK_MAX_RT                                   | 4      | 0            | R/W         | Mask interrupt caused by MAX_RT  1: Interrupt not reflected on the IRQ pin  0: Reflect MAX_RT as active low interrupt on the IRQ pin. |  |  |  |  |  |

|   |             | EN_CRC                                        | 3      | 0            | R/W         | Enable CRC. Forced high if one of the bits in the EN_AA is high.                                                                      |  |  |  |  |  |

|   |             | CRCO                                          | 2      | 0            | R/W         | CRC encoding scheme '0' - 1 byte '1' - 2 bytes                                                                                        |  |  |  |  |  |

|   |             | PWR_UP                                        | 1      | 0            | R/W         | 1: POWER UP, 0:POWER DOWN                                                                                                             |  |  |  |  |  |

|   |             | PRIM_RX                                       | 0      | 0            | R/W         | RX/TX control<br>1: PRX, 0: PTX                                                                                                       |  |  |  |  |  |

|   |             | Enable 'Auto Acknowledgment' Function Disable |        |              |             |                                                                                                                                       |  |  |  |  |  |

|   |             |                                               |        | 1            |             | with nRF2401, see 說明 1.                                                                                                               |  |  |  |  |  |

|   |             | Reserved                                      | 7:6    | 00           |             | Only '00' allowed                                                                                                                     |  |  |  |  |  |

|   |             | ENAA_P5                                       | 5      | 1            | R/W         | Enable auto acknowledgement data pipe 5                                                                                               |  |  |  |  |  |

|   | 01          | ENAA_P4                                       | 4      | 1            | R/W         | Enable auto acknowledgement data pipe 4                                                                                               |  |  |  |  |  |

|   |             | ENAA_P3                                       | 3      | 1            | R/W         | Enable auto acknowledgement data pipe 3                                                                                               |  |  |  |  |  |

|   |             | ENAA_P2                                       | 2      | 1            | R/W         | Enable auto acknowledgement data pipe 2                                                                                               |  |  |  |  |  |

|   |             | ENAA_P1                                       | 1      | 1            | R/W         | Enable auto acknowledgement data pipe 1                                                                                               |  |  |  |  |  |

|   |             | ENAA_P0                                       | 0      | 1            | R/W         | Enable auto acknowledgement data pipe 0                                                                                               |  |  |  |  |  |

|   |             |                                               | EN_R   | XADDR        | Enab        | led RX Addresses                                                                                                                      |  |  |  |  |  |

|   | 02          | Reserved                                      | 7:6    | 00           | R/W         | Only '00' allowed.                                                                                                                    |  |  |  |  |  |

|   |             | ERX_P5                                        | 5      | 0            | R/W         | Enable data pipe 5                                                                                                                    |  |  |  |  |  |

|   |             | •                                             |        |              |             |                                                                                                                                       |  |  |  |  |  |

|    | ERX_P4   | 4       | 0       | R/W        | Enable data pipe 4                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|----|----------|---------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|    | ERX_P3   | 3       | 0       | R/W        | Enable data pipe 3                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|    | ERX_P2   | 2       | 0       | R/W        | Enable data pipe 2                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|    | ERX_P1   | 1       | 1       | R/W        | Enable data pipe 1                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|    | ERX_P4   | 0       | 1       | R/W        | Enable data pipe 0                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|    |          |         |         |            |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|    | Reserved | 7:2     | 000000  | R/W        | Only '000000' allowed.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 03 | AW       | 1:0     | 11      | R/W        | RX/TX Address field width '00' - Illegal '01' - 3 bytes '10' - 4 bytes '11' - 5 bytes LSByte is used if address width is below 5 bytes.                                                                                                                                                                                   |  |  |  |  |  |  |

|    | SI       | ETUP_RE | TR      | Setup of A | utomatic Retransmission                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 04 | ARD      | 7:4     | 0000    | R/W        | Auto Retransmit Delay '0000' – Wait 250μS '0001' – Wait 500μS '0010' – Wait 750μS '1111' – Wait 4000μS (Delay defined from end of transmission to start of next transmission).  Auto Retransmit Count '0000' –Re-Transmit disabled '0001' – Up to 1 Re-Transmit on fail of AA '1111' – Up to 15 Re-Transmit on fail of AA |  |  |  |  |  |  |

|    |          |         | RF_CI   | H RI       | Channel                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 05 | Reserved | 7       | 0       |            | Only '0' allowed.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|    | RF_CH    | 6:0     | 0000010 | R/W        | Sets the frequency channel nRF24L01 operates on.                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|    |          | R       | F_SETUP | RF         | Setup Register                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| <  | Reserved | 7:5     | 000     | R/W        | Only '000' allowed.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|    | PLL_LOCK | 4       | 0       | R/W        | Force PLL lock signal. Only used in test.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 06 | RF_DR    | 3       | 1       | R/W        | Air Data Rate '0' – 1Mbps '1' – 2Mbps                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|    | RF_PWR   | 2:1     | 11      | R/W        | Set RF output power in TX mode '00'18dBm '01'12dBm                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|    |                                                                                                 |     |        |     | '10' 6dPm                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------|-----|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|    |                                                                                                 |     |        |     | '10' – -6dBm                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |                                                                                                 | _   | _      |     | '11' – 0dBm                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|    | LNA_HCURR                                                                                       | 0   | 1      | R/W | Setup LNA gain                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|    | STATUS Status Register (In parallel to the SPI command word applied on the MOSI pin, the STATUS |     |        |     |                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|    | register is shifted serially out on the MISO pin)                                               |     |        |     |                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|    | Reserved                                                                                        | 7   | 0      | R/W | Only '0' allowed.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|    | RX_DR                                                                                           | 6   | 0      | R/W | Data Ready RX FIFO interrupt. Asserted when new data arrives RX FIFOb.  Write 1 to clear bit.                                                                                                                                                                                                   |  |  |  |  |  |  |

| 07 | TX_DS                                                                                           | 5   | 0      | R/W | Data Sent TX FIFO interrupt. Asserted when packet transmitted on TX. If AUTO_ACK is activated, this bit is set high only when ACK is received.  Write 1 to clear bit.                                                                                                                           |  |  |  |  |  |  |

|    | MAX_RT                                                                                          | 4   | 0      | R/W | Maximum number of TX retransmits interrupt Write 1 to clear bit. If MAX_RT is asserted it must be cleared to enable further communication.                                                                                                                                                      |  |  |  |  |  |  |

|    | RX_P_NO                                                                                         | 3:1 | 111    | R   | Data pipe number for the payload available for reading from RX_FIFO 000-101: Data Pipe Number 110: Not Used 111: RX FIFO Empty.                                                                                                                                                                 |  |  |  |  |  |  |

|    | TX_FULL                                                                                         | 0   | 0      | R   | TX FIFO full flag. 1: TX FIFO full. 0: Available locations in TX FIFO.                                                                                                                                                                                                                          |  |  |  |  |  |  |

|    | OBSERVE_TX Transmit observe register                                                            |     |        |     |                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 08 | PLOS_CNT                                                                                        | 7:4 | 0      | R   | Count lost packets. The counter is overflow protected to 15, and discontinues at max until reset. The counter is reset by writing to RF_CH.                                                                                                                                                     |  |  |  |  |  |  |

|    | ARC_CNT                                                                                         | 3:0 | 0      | R   | Count retransmitted packets. The counter is reset when transmission of a new packet starts.                                                                                                                                                                                                     |  |  |  |  |  |  |

|    |                                                                                                 |     |        | CD  |                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 09 | Reserved                                                                                        | 7:1 | 000000 | R   | device does not succeed to get packets through, as indicated by the MAX_RT IRQ for single packets and by the packet loss counter (PLOS_CNT) if several packets are lost. If the PLOS_CNT in the PTX device indicates a high rate of packet losses, the device can be configured to a PRX device |  |  |  |  |  |  |

|           |               |      |             |         | $130\mu s + 128\mu s = 258\mu s$ ) to check CD. If CD was high (jam situation), the frequency |

|-----------|---------------|------|-------------|---------|-----------------------------------------------------------------------------------------------|

|           |               |      |             |         | channel should be changed. If CD was low                                                      |

|           |               |      |             |         | (out of range or jammed by broadband                                                          |

|           |               |      |             |         | signals like WLAN), it may continue on the                                                    |

|           |               |      |             |         | same frequency channel, but you must                                                          |

|           |               |      |             |         | perform other adjustments (a dummy write                                                      |

|           |               |      |             |         | to the RF_CH clears the PLOS_CNT)                                                             |

|           | CD            | 0    | 0           |         |                                                                                               |

|           |               |      |             |         | Receive address data pipe 0. 5 Bytes                                                          |

| 0.1       |               |      | 0xE7E7E     |         | maximum length. (LSByte is written first.                                                     |

| 0A        | RX_ADDR_P0    | 39:0 | 7E7E7       | R/W     | Write the number of bytes defined by                                                          |

|           |               |      |             |         | SETUP_AW)                                                                                     |

|           |               |      | 0. G2G2     |         | Receive address data pipe 1. 5 Bytes                                                          |

| OD        | DV ADDD D1    | 39:0 | 0xC2C2      | R/W     | maximum length. (LSByte is written first.                                                     |

| 0B        | RX_ADDR_P1    |      | C<br>2C2C2  | R/W     | Write the number                                                                              |

|           |               |      | 2C2C2       |         | of bytes defined by SETUP_AW)                                                                 |

| 0C        | RX_ADDR_P2    | 7:0  | 0xC3        | R/W     | Receive address data pipe 2. Only LSB.                                                        |

| 00        | KA_ADDK_I 2   | 7.0  | OAC3        |         | MSBytes is equal to RX_ADDR_P1[39:8]                                                          |

| 0D        | RX_ADDR_P3    | 7:0  | 0xC4        | R/W     | Receive address data pipe 3. Only LSB.                                                        |

| UD        | ICAL_ADDIC_13 | 7.0  | oxe i       | 10 11   | MSBytes is equal to RX_ADDR_P1[39:8]                                                          |

| 0E        | RX_ADDR_P4    | 7:0  | 0xC5        | R/W     | Receive address data pipe 4. Only LSB.                                                        |

| OL        |               |      |             |         | MSBytes is equal to RX_ADDR_P1[39:8]                                                          |

| 0F        | RX_ADDR_P5    | 7:0  | 0xC6        | R/W     | Receive address data pipe 5. Only LSB.                                                        |

| <b>O1</b> |               |      |             |         | MSBytes is equal to RX_ADDR_P1[39:8]                                                          |

|           |               |      | <b>4.</b> C |         | Transmit address. Used for a PTX device                                                       |

|           |               |      | 0 15555     |         | only.(LSByte is written first)                                                                |

| 10        | TX_ADDR       | 39:0 | 0xE7E7E     | R/W     | Set RX_ADDR_P0 equal to this address to                                                       |

|           |               |      | 7E7E7       |         | handle automatic acknowledge if this is a PTX device with Enhanced ShockBurst <sup>TM</sup>   |

|           |               |      |             |         | enabled.                                                                                      |

|           |               |      |             |         |                                                                                               |

|           |               | 1    | Ι           | RX_PW_P |                                                                                               |

|           | Reserved      | 7:6  |             | R/W     | Only '00' allowed.                                                                            |

| 11        |               |      |             |         | Number of bytes in RX payload in data pipe                                                    |

|           | RX_PW_P0      | 5:0  |             | R/W     | 0 (1to 32 bytes).                                                                             |

|           |               |      |             |         | 0 Pipe not used 1 = 1 byte                                                                    |

|           | ×             |      |             |         | 32 = 32 bytes                                                                                 |

| 12        |               | ı    | 1           | RX_PW_P | 1                                                                                             |

| 12        | Reserved      | 7:6  | 00          | R/W     | Only '00' allowed.                                                                            |

|           |               |      |             |         | Number of bytes in RX payload in data pipe                                                    |

|           | RX_PW_P1      | 5:0  | 00          | R/W     | 1 (1to 32 bytes).                                                                             |

|           |               |      |             |         | 0 Pipe not used                                                                               |

|    |          |      |         |         | 1 – 1 h. 4.                                                                                                                                                                                                                    |  |  |  |  |

|----|----------|------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|    |          |      |         |         | 1 = 1 byte<br>32 = 32 bytes                                                                                                                                                                                                    |  |  |  |  |

|    |          |      |         | RX_PW_I | •                                                                                                                                                                                                                              |  |  |  |  |

|    | Reserved | 7:6  | 00      | R/W     | Only '00' allowed.                                                                                                                                                                                                             |  |  |  |  |

| 13 | RX_PW_P2 | 5:0  | 0       | R/W     | Number of bytes in RX payload in data pipe 2 (1to 32 bytes).  0 Pipe not used1 = 1 byte  32 = 32 bytes                                                                                                                         |  |  |  |  |

|    |          |      |         | RX_PW_I |                                                                                                                                                                                                                                |  |  |  |  |

|    | Reserved | 7:6  | 00      | R/W     | Only '00' allowed                                                                                                                                                                                                              |  |  |  |  |

| 14 | RX_PW_P3 | 5:0  | 0       | R/W     | Number of bytes in RX payload in data pipe 3 (1to 32 bytes).  0 Pipe not used  1 = 1 byte  32 = 32 bytes                                                                                                                       |  |  |  |  |

|    |          |      |         | RX_PW_I | 24                                                                                                                                                                                                                             |  |  |  |  |

|    | Reserved | 7:6  | 00      | R/W     | Only '00' allowed.                                                                                                                                                                                                             |  |  |  |  |

| 15 | RX_PW_P4 | 5:0  | 0       | R/W     | Number of bytes in RX payload in data pipe 4 (1to 32 bytes).  0 Pipe not used 1 = 1 byte  32 = 32 bytes                                                                                                                        |  |  |  |  |

|    | RX_PW_P5 |      |         |         |                                                                                                                                                                                                                                |  |  |  |  |

|    | Reserved | 7:6  | 00      | R/W     | Only '00' allowed.                                                                                                                                                                                                             |  |  |  |  |

| 16 | RX_PW_P5 | 5:0  | 0       | R/W     | Number of bytes in RX payload in data pipe 5 (1to 32 bytes).  0 Pipe not used 1 = 1 byte  32 = 32 bytes                                                                                                                        |  |  |  |  |

|    | A        | FIFO | _STATUS | FIF     | O Status Register                                                                                                                                                                                                              |  |  |  |  |

|    | Reserved | 7    | 0       | R/W     | Only '0' allowed.                                                                                                                                                                                                              |  |  |  |  |

| 17 | TX_REUSE | 6    | 0       | R       | Reuse last transmitted data packet if set high. The packet is repeatedly retransmitted as long as <b>CE</b> is high. TX_REUSE is set by the SPI command REUSE_TX_PL, and is reset by the SPI commands W_TX_PAYLOAD or FLUSH TX |  |  |  |  |

|    | TX_FULL  | 5    | 0       | R       | TX FIFO full flag. 1: TX FIFO full. 0: Available locations in TX FIFO.                                                                                                                                                         |  |  |  |  |

|    | TX_EMPTY | 4    | 1       | R       | TX FIFO empty flag  1: TX FIFO empty  0: Data in TX FIFO                                                                                                                                                                       |  |  |  |  |

|    | Reserved | 3:2  | 00      | R/W     | Only '00' allowed.                                                                                                                                                                                                             |  |  |  |  |

| - |      |                                      |       |            |                  |                                              |  |  |  |  |  |

|---|------|--------------------------------------|-------|------------|------------------|----------------------------------------------|--|--|--|--|--|

|   |      |                                      |       |            |                  | RX FIFO full flag                            |  |  |  |  |  |

|   |      | RX_FULL                              | 1     | 0          | R                | 1: RX FIFO full                              |  |  |  |  |  |

|   |      |                                      |       |            |                  | 0: Available locations in RX FIFO            |  |  |  |  |  |

|   |      | RX_EMPTY                             |       |            |                  | RX FIFO empty flag                           |  |  |  |  |  |

|   |      |                                      | 0     | 1          | R                | 1: RX FIFO empty                             |  |  |  |  |  |

|   |      |                                      |       |            |                  | 0: Data in RX FIFO                           |  |  |  |  |  |

|   |      |                                      |       |            |                  | Written by separate SPI command ACK          |  |  |  |  |  |

|   |      |                                      |       |            |                  | packet payload to data pipe number PPP       |  |  |  |  |  |

|   | N/A  | ACK_PLDc                             | 255:0 | X          | W                | given in SPI command Used in RX mode         |  |  |  |  |  |

|   |      | NCK_I LDC                            | 233.0 | 71         | **               | only Maximum three ACK packet payloads       |  |  |  |  |  |

|   |      |                                      |       |            |                  | can be pending. Payloads with same PPP are   |  |  |  |  |  |

|   |      |                                      |       |            |                  | handled first in first out.                  |  |  |  |  |  |

|   |      |                                      |       |            | W                | Written by separate SPI command TX data      |  |  |  |  |  |

|   | N/A  | TX_PLD                               | 255:0 | X          |                  | payload register 1 - 32 bytes.               |  |  |  |  |  |

|   |      |                                      | 233.0 | Λ          |                  | This register is implemented as a FIFO with  |  |  |  |  |  |

|   |      |                                      |       |            |                  | three levels. Used in TX mode only.          |  |  |  |  |  |

|   |      |                                      |       |            |                  | Read by separate SPI command RX data         |  |  |  |  |  |

|   | N/A  |                                      | 255:0 | X          | R                | payload register. 1 - 32 bytes.              |  |  |  |  |  |

|   | 11/1 | RX_PLD                               |       |            |                  | This register is implemented as a FIFO with  |  |  |  |  |  |

|   |      |                                      |       |            |                  | three levels. All RX channels share the same |  |  |  |  |  |

|   |      |                                      |       |            |                  | FIFO                                         |  |  |  |  |  |

|   |      | DYNPDc Enable dynamic payload length |       |            |                  |                                              |  |  |  |  |  |

|   |      | Reserved                             | 7:6   | 0          | R/W              | Only '00' allowed.                           |  |  |  |  |  |

|   |      |                                      |       | 0          | DAY              | Enable dyn. payload length data pipe 5.      |  |  |  |  |  |

|   |      | DPL_P5                               | 5     | 0          | R/W              | (Requires EN_DPL and ENAA_P5)                |  |  |  |  |  |

|   |      |                                      |       | <b>*</b> C | DAY              | Enable dyn. payload length data pipe 4.      |  |  |  |  |  |

|   | 1C   | DPL_P4                               | 4     | 0          | R/W              | (Requires EN_DPL and ENAA_P4)                |  |  |  |  |  |

|   |      |                                      |       |            |                  | Enable dyn. payload length data pipe 3.      |  |  |  |  |  |

|   |      | DPL_P3                               | 3     | 0          | R/W              | (Requires EN_DPL and ENAA_P3)                |  |  |  |  |  |

|   |      |                                      |       |            |                  | Enable dyn. payload length data pipe 2.      |  |  |  |  |  |

|   |      | DPL_P2                               | 2     | 0          | R/W              | (Requires EN_DPL and ENAA_P2)                |  |  |  |  |  |

|   |      |                                      |       |            |                  | Enable dyn. payload length data pipe 1.      |  |  |  |  |  |

|   |      | DPL_P1                               | 1     | 0          | R/W              | (Requires EN_DPL and ENAA_P1)                |  |  |  |  |  |

|   |      |                                      |       |            |                  | Enable dyn. payload length data pipe 0.      |  |  |  |  |  |

|   |      | DPL_P0                               | 0     | 0          | R/W              | (Requires EN_DPL and ENAA_P0)                |  |  |  |  |  |

|   |      |                                      | ]     | FEATURE    | Ec Feat          | ture Register                                |  |  |  |  |  |

|   |      | Reserved                             | 7:3   | 0          | R/W              | Only '00000' allowed.                        |  |  |  |  |  |

|   | 1D   | EN_DPL                               | 2     | 0          | R/W              | Enables Dynamic Payload Length               |  |  |  |  |  |

|   | TD   | EN_ACK_PAYd                          | 1     | 0          | R/W              | Enables Payload with ACK                     |  |  |  |  |  |

|   |      | EN_DYN_ACK                           | 0     | 0          | R/W              | Enables the W_TX_PAYLOAD_NOACK               |  |  |  |  |  |

|   |      | LILDIN_ACK                           | 0     | U          | 1\(\frac{1}{2}\) | command.                                     |  |  |  |  |  |

| _ |      |                                      |       |            |                  | · · · · · · · · · · · · · · · · · · ·        |  |  |  |  |  |

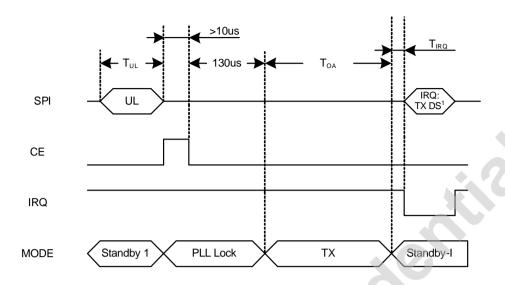

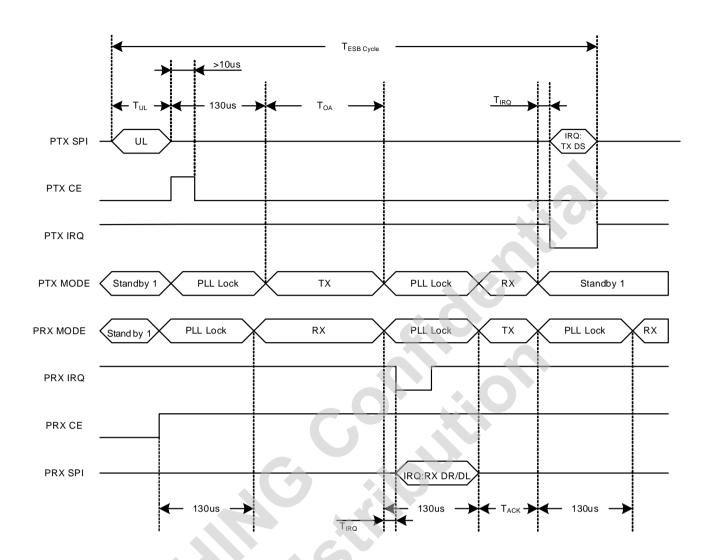

## Enhanced ShockBurst™ Transmitting Payload

- 1. The configuration bit PRIM\_RX has to be low.

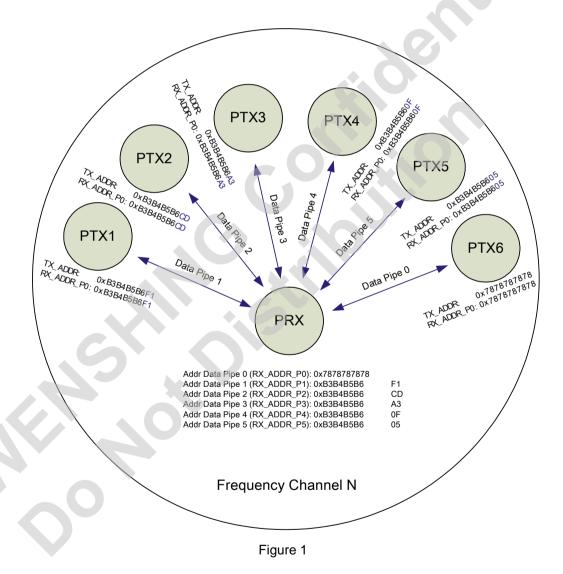

- 2. When the application MCU has data to transmit, the address for the receiving node (TX\_ADDR) and payload data (TX\_PLD) has to be clocked into nRF24L01 through the SPI. The width of TXpayload is counted from number of bytes written into the TX FIFO from the MCU. TX\_PLD must be written continuously while holding CSN low. TX\_ADDR does not have to be rewritten if it is unchanged from last transmit. If the PTX device shall receive acknowledge, data pipe 0 has to be configured to receive the ACK packet. The RX address for data pipe 0 (RX\_ADDR\_P0) has to be equal to the TX address (TX\_ADDR) in the PTX device. For the example in Figure 1

the following address settings have to be performed for the TX5 device and the RX device:

TX5 device: TX\_ADDR = 0xB3B4B5B605

TX5 device: RX\_ADDR\_P0 = 0xB3B4B5B605

RX device: RX ADDR P5 = 0xB3B4B5B605

3. A high pulse on  ${\mbox{\bf CE}}$  starts the transmission. The minimum pulse width on  ${\mbox{\bf CE}}$  is 10 $\mu s$ .

- 4. nRF24L01 ShockBurst™:

- Radio is powered up.

- □ 16MHz internal clock is started.

- RF packet is completed (see the packet description).

- Data is transmitted at high speed (1Mbps or 2Mbps configured by MCU).

- 5. If auto acknowledgement is activated (ENAA\_P0=1) the radio goes into RX mode immediately, unless the NO\_ACK bit is set in the received packet. If a valid packet has been received in the valid acknowledgement time window, the transmission is considered a success. The TX\_DS bit in the STATUS register is set high and the payload is removed from TX FIFO. If a valid ACK packet is not received in the specified time window, the payload is retransmitted (if auto retransmit is enabled). If the auto retransmit counter (ARC\_CNT) exceeds the programmed maximum limit (ARC), the MAX\_RT bit in the STATUS register is set high. The payload in TX FIFO is NOT removed. The IRQ pin is active when MAX\_RT or TX\_DS is high. To turn off the IRQ pin, the interrupt source must be reset by writing to the STATUS register (see Interrupt chapter). If no ACK packet is received for a packet after the maximum number of retransmits, no further packets can be transmitted before the MAX\_RT interrupt is cleared. The packet loss counter (PLOS\_CNT) is incremented at each MAX\_RT interrupt. That is, ARC\_CNT counts the number of retransmits that was required to get a single packet through. PLOS\_CNT counts the number of packets that did not get through after maximum number of retransmits.

- 6. nRF24L01 goes into standby-I mode if **CE** is low. Otherwise next payload in TX FIFO is transmitted. If TX FIFO is empty and **CE** is still high, nRF24L01 enters standby-II mode.

- 7. If nRF24L01 is in standby-II mode, it goes to standby-I mode immediately if **CE** is set low.

#### Enhanced ShockBurst™ Receive Payload

- 1. RX is selected by setting the PRIM\_RX bit in the CONFIG register to high. All data pipes that receive data must be enabled (EN\_RXADDR register), auto acknowledgement for all pipes running Enhanced ShockBurst™ has to be enabled (EN\_AA register), and the correct payload widths must be set (RX\_PW\_Px registers). Addresses have to be set up as described in item 2 in the Enhanced ShockBurst™ transmit payload chapter above.

- 2. Active RX mode is started by setting CE high.

- 3. After 130µs nRF24L01 is monitoring the air for incoming communication.

- 4. When a valid packet has been received (matching address and correct CRC), the payload is stored in the RX-FIFO, and the RX\_DR bit in STATUS register is set high. The IRQ pin is active Revision 2.0 Page 66 of 74 when RX\_DR is high. RX\_P\_NO in STATUS register indicates what data pipe the payload has been received in.

- 5. If auto acknowledgement is enabled, an ACK packet is transmitted back, unless the NO\_ACK bit is set in the received packet. If there is a payload in the TX\_PLD FIFO, this payload is added to the ACK packet.

- 6. MCU sets the **CE** pin low to enter standby-I mode (low current mode).

- 7. MCU can clock out the payload data at a suitable rate through the SPI.

- 8. nRF24L01 is now ready for entering TX or RX mode or power down mode.

## State diagram

1 IRQ if No Ack is on.

$T_{IRQ} = 8.2 \eta s @ 1Mbps, T_{IRQ} = 6.0 \eta s @ 2Mbps$

# Transmitting one packet with NO\_ACK on

通訊範例 1: 當要對 2.4GHz 傳送 DATA,長度 XX,暫存器為下表:

| 位址 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

|----|----|----|----|----|----|----|----|----|

| 數據 |    |    |    |    |    |    |    |    |

| 位址 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

| 數據 |    |    |    |    |    |    |    |    |

| 位址 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 數據 |    |    |    |    |    |    |    |    |

| 位址 | 18 | 19 | 1A | 1B | 1C | 1D |    |    |

| 數據 |    |    |    |    |    |    |    |    |

Timing of Enhanced ShockBurst™ for one packet upload (2Mbps)

通訊範例 2: 當要對 2.4GHz 傳送 DATA,長度 XX,暫存器為下表:

| 位址 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

|----|----|----|----|----|----|----|----|----|

| 數據 |    |    |    |    |    |    |    |    |

| 位址 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

| 數據 |    |    |    |    |    |    |    |    |

| 位址 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 數據 |    |    |    |    |    |    |    |    |

| 位址 | 18 | 19 | 1A | 1B | 1C | 1D |    |    |

| 數據 |    |    |    |    |    |    |    |    |

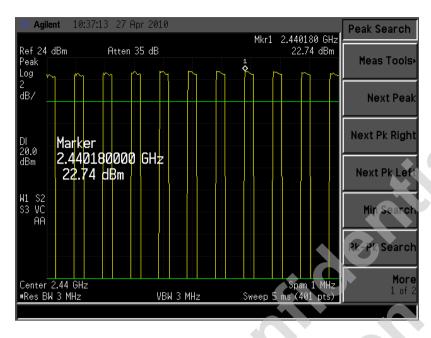

#### **Output Power**

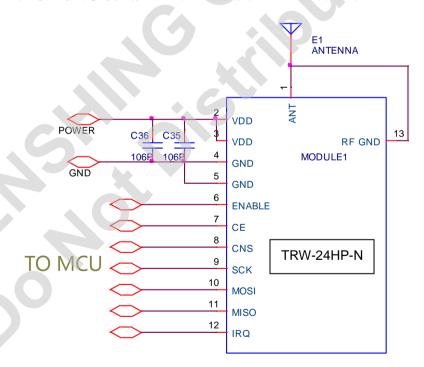

### Layout 注意事項

1. 在電源供應前最好多併幾個大電容,可提高 RF 通訊的穩定性。

- 2. 模組底部基板最好不要設計數位信號,以避免 EMI 傳導到 RF 模組內。

- 3. 模組外接天線,天線部份的 PCB 需盡可能給予無銅箔區域,以做天線幅射之用。

- 4. 如使用模組內的端子連接外部天線,模組之 ANT PIN 及 RF GND PIN 不可焊到 PCB。